대만 파운드리(반도체 위탁생산) 업체 TSMC가 차세대 인공지능(AI) 칩의 핵심 기술로 꼽히는 '실리콘 포토닉스' 분야 특허를 빠르게 확보하며 시장 선점에 나섰다. 세계 1위 파운드리 지위를 굳히려는 전략으로 풀이된다.

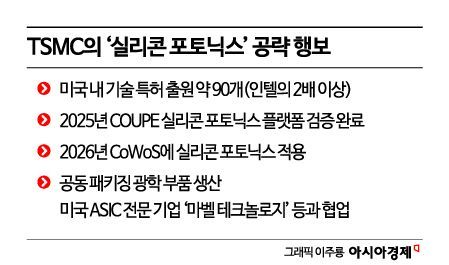

8일 대만 이코노믹데일리뉴스 등 현지 언론은 일본 보도를 인용해 TSMC가 미국에서 실리콘 포토닉스 관련 특허 출원을 대폭 늘리고 있다고 전했다. 올해 현재까지 출원 건수는 인텔의 2배 이상으로, 2023년 양 사 간 격차가 크지 않았던 것과 비교해 급격한 증가세다.

실리콘 포토닉스는 반도체 칩 안에서 신호를 전기가 아니라 빛으로 주고받는 기술이다. 전기는 전선 내부에서 원자와 충돌하며 속도가 줄지만, 빛은 초당 30만㎞ 속도로 직진해 데이터 전송을 훨씬 빠르고 효율적으로 처리할 수 있다.

TSMC는 이 기술을 자사 고급 패키징(CoWoS) 공정에 적용해 '공동패키징형광학(CPO)'을 상용화할 계획이다. 업계는 이 기술이 엔비디아가 내년 출시를 준비 중인 차세대 그래픽처리장치(GPU) '루빈'에도 활용돼 성능 향상을 이끌 것으로 보고 있다.

TSMC와 삼성전자 등 글로벌 파운드리 기업들은 최근 이 기술을 기반으로 한 CPO를 상용화하기 위해 연구개발(R&D)에 매진해 온 것으로 전해진다. 엔비디아 등 고객사들이 향후에 만들고자 하는 AI 칩의 데이터 전송량과 속도는 빠르게 높아지고 있고, 이를 구현하기 위해선 실리콘 포토닉스를 활용한 CPO 개발이 절대적으로 필요하다고 판단했기 때문이다.

특히 TSMC가 최근 이 기술에 열의를 쏟고 있어 업계의 큰 주목을 받고 있다. 거금을 투자하는 것은 물론 지난 4월 미국 캘리포니아 샌타클래라에서 열린 '북미 기술 포럼'에선 실리콘 포토닉스 기술을 각종 공정에 통합해 활용하겠단 청사진을 밝히기도 했다. 구체적으론, 올해 포토닉 다이 위에 전자 다이를 쌓는 '쿠페(COUPE)'에 대한 검증을 끝내고 내년에는 자사의 고급 패키징 기술인 '칩 온 웨이퍼 온 서브스트레이트(CoWoS)'에 실리콘 포토닉스를 적용해 '공동 패키징 광학 부품'을 만들겠다고 강조했다. 또한 TSMC는 실리콘 포토닉스 기술 관련 시장 확대에 대응하고 3㎚(1㎚=10억분의 1m) 이하 공정에서의 차세대 실리콘 포토닉스 기술을 개발하기 위해 미국의 주문형 반도체(ASIC), 고속 네트워크 칩 전문 기업인 '마벨 테크놀로지'와도 협력하고 있다.

TSMC의 실리콘 포토닉스 기술이 고도화될수록 '큰 손' 고객인 엔비디아의 차세대 AI 칩 양산과 출시도 빨라질 것으로 업계는 내다보고 있다. 엔비디아 내부에서도 CoWoS 등 2.5D, 3D 패키징을 활용해 내년에 출시될 예정인 AI GPU '루빈'에 실리콘 포토닉스 기술을 대량으로 도입하기로 방침을 세운 것으로 전해졌다. 이를 통해 엔비디아는 전기를 통한 칩 간 연결로 일어나는 병목 현상과 전력 과소비 문제 등을 해결할 수 있길 기대하고 있다.

대만 이코노믹데일리뉴스=윈 후이종, 리 멍산 기자/번역=아시아경제

※이 칼럼은 아시아경제와 대만 이코노믹데일리뉴스의 전략적 제휴를 통해 게재되었음을 알립니다.

김형민 기자 khm193@asiae.co.kr

![[포토] 예지원, 전통과 현대가 공존한 화보 공개](https://image.ajunews.com/content/image/2025/10/09/20251009182431778689.jpg)

![블랙핑크 제니, 최강매력! [포토]](https://file.sportsseoul.com/news/cms/2025/09/05/news-p.v1.20250905.ed1b2684d2d64e359332640e38dac841_P1.jpg)

![[포토]두산 안재석, 관중석 들썩이게 한 끝내기 2루타](https://file.sportsseoul.com/news/cms/2025/08/28/news-p.v1.20250828.1a1c4d0be7434f6b80434dced03368c0_P1.jpg)

![[포토] 발표하는 김정수 삼양식품 부회장](https://image.ajunews.com/content/image/2025/11/03/20251103114206916880.jpg)

![블랙핑크 제니, 매력이 넘쳐! [포토]](https://file.sportsseoul.com/news/cms/2025/09/05/news-p.v1.20250905.c5a971a36b494f9fb24aea8cccf6816f_P1.jpg)

![[포토] '삼양1963 런칭 쇼케이스'](https://image.ajunews.com/content/image/2025/11/03/20251103114008977281.jpg)

![[포토] 박지현 '순백의 여신'](http://www.segye.com/content/image/2025/09/05/20250905507414.jpg)

![[포토] 키스오브라이프 하늘 '완벽한 미모'](http://www.segye.com/content/image/2025/09/05/20250905504457.jpg)

![[포토] 아이들 소연 '매력적인 눈빛'](http://www.segye.com/content/image/2025/09/12/20250912508492.jpg)

![[포토]첫 타석부터 안타 치는 LG 문성주](https://file.sportsseoul.com/news/cms/2025/09/02/news-p.v1.20250902.8962276ed11c468c90062ee85072fa38_P1.jpg)

![[포토] 국회 예결위 참석하는 김민석 총리](https://cphoto.asiae.co.kr/listimg_link.php?idx=2&no=2025110710410898931_1762479667.jpg)

![[포토] 박지현 '아름다운 미모'](http://www.segye.com/content/image/2025/11/19/20251119519369.jpg)

![[포토] 김고은 '단발 여신'](http://www.segye.com/content/image/2025/09/05/20250905507236.jpg)

![[작아진 호랑이③] 9위 추락 시 KBO 최초…승리의 여신 떠난 자리, KIA를 덮친 '우승 징크스'](http://www.sportsworldi.com/content/image/2025/09/04/20250904518238.jpg)

![[포토] 알리익스프레스, 광군제 앞두고 팝업스토어 오픈](https://cphoto.asiae.co.kr/listimg_link.php?idx=2&no=2025110714160199219_1762492560.jpg)

![[포토]끝내기 안타의 기쁨을 만끽하는 두산 안재석](https://file.sportsseoul.com/news/cms/2025/08/28/news-p.v1.20250828.0df70b9fa54d4610990f1b34c08c6a63_P1.jpg)

![[포토] 키스오브라이프 쥴리 '단발 여신'](http://www.segye.com/content/image/2025/09/05/20250905504358.jpg)

![[포토] 한샘, '플래그십 부산센텀' 리뉴얼 오픈](https://image.ajunews.com/content/image/2025/10/31/20251031142544910604.jpg)

![[포토] 언론 현업단체, "시민피해구제 확대 찬성, 권력감시 약화 반대"](https://image.ajunews.com/content/image/2025/09/05/20250905123135571578.jpg)

![[포토]두산 안재석, 연장 승부를 끝내는 2루타](https://file.sportsseoul.com/news/cms/2025/08/28/news-p.v1.20250828.b12bc405ed464d9db2c3d324c2491a1d_P1.jpg)

![[포토] 김고은 '상연 생각에 눈물이 흘러'](http://www.segye.com/content/image/2025/09/05/20250905507613.jpg)

![[포토] 아홉 '신나는 컴백 무대'](http://www.segye.com/content/image/2025/11/04/20251104514134.jpg)

![[포토] TXT 범규 '반가운 손인사'](http://www.segye.com/content/image/2025/11/05/20251105518398.jpg)

![[칩톡]'AI 신흥강자' 딥엑스…"글로벌 표준 노린다"](https://cphoto.asiae.co.kr/listimg_link.php?idx=2&no=2025112814573936291_1764309459.jpg)